# Design and implementation of floating field ring edge termination on vertical geometry $\beta$ -Ga<sub>2</sub>O<sub>3</sub> rectifiers

Cite as: J. Vac. Sci. Technol. A **38**, 063414 (2020); https://doi.org/10.1116/6.0000693 Submitted: 06 October 2020 . Accepted: 02 November 2020 . Published Online: 17 November 2020

🗓 Ribhu Sharma, Minghan Xian, Mark E. Law, 🗓 Marko Tadjer, 🗓 Fan Ren, and 🗓 Stephen J. Pearton

# Design and implementation of floating field ring edge termination on vertical geometry β-Ga<sub>2</sub>O<sub>3</sub> rectifiers

Cite as: J. Vac. Sci. Technol. A 38, 063414 (2020); doi: 10.1116/6.0000693 Submitted: 6 October 2020 · Accepted: 2 November 2020 · Published Online: 17 November 2020

Ribhu Sharma, 1 D Minghan Xian, 2 Mark E. Law, 1 Marko Tadjer, 3 D Fan Ren, 2 D and Stephen J. Pearton 4.a) D

## **AFFILIATIONS**

- <sup>1</sup>Department of Electrical and Computer Engineering, University of Florida, Gainesville, Florida 32611

- <sup>2</sup>Department of Chemical Engineering, University of Florida, Gainesville, Florida 32611

- <sup>3</sup>U.S. Naval Research Laboratory, 4555 Overlook Ave SW, Washington, DC 20375

Note: This paper is part of the Special Topic Collection on Gallium Oxide Materials and Devices.

a)Electronic mail: spear@mse.ufl.edu

#### **ABSTRACT**

One of the key areas for implementation of high-power Ga<sub>2</sub>O<sub>3</sub> rectifiers is the mitigation of electric field crowding at the edge of the depletion region to avoid premature breakdown. Floating metal field rings (FMRs) are a relatively simple approach for achieving this. We report simulations of the spacing  $(1-10\,\mu\text{m})$ , width  $(2-15\,\mu\text{m})$ , number of rings, and also the effect of biasing the rings  $(0-280\,\text{V})$  and including a field plate at the periphery of the rings on the breakdown voltage of a vertical geometry rectifier with a range of doping concentrations  $(5 \times 10^{15} - 4 \times 10^{16} \text{ cm}^{-3})$  in the drift region. Improvements in breakdown voltage of 19%–54% relative to an unterminated rectifier are found with an optimum design of the field rings. The experimental results on rectifiers with different FMR geometries show an  $R_{ON}$  of 4.5–4.9 m $\Omega$  cm<sup>2</sup>, a turn-on voltage of 0.96–0.94 V, a high on-off ratio of >5 × 10<sup>6</sup>, an ideality factor of 1.03, and a Schottky barrier height of 1.03 eV at room temperature. These devices have similar forward electrical characteristics, indicating that FMRs do not degrade the device rectifying performance.

Published under license by AVS. https://doi.org/10.1116/6.0000693

# I. INTRODUCTION

The development of high-power devices using Ga<sub>2</sub>O<sub>3</sub> has attracted much recent attention for the goal of reducing the size and weight while simultaneously increasing the power capability of electronics beyond current devices based on silicon. 1-8 bandgap of β-Ga<sub>2</sub>O<sub>3</sub> is 4.8-4.9 eV, and the breakdown field is estimated to be 8 MV/cm, about three times larger than that of 4H-SiC and GaN. 1-8 A key factor in determining switching losses in power electronics is the on-state resistance, whose optimization is always a strong driving factor in the move to ultrawide bandgap The on-state resistance can be derived from semiconductors.9the Poisson equation in one-dimension as<sup>1</sup>

$$R_{\rm ON} = (4V_{\rm R}^2)/(\mu \epsilon E_{\rm C}^3), \tag{1}$$

where V<sub>B</sub> is the breakdown voltage, µ is the majority carrier mobility,  $\varepsilon$  is the permittivity of the semiconductor, and  $E_C$  is the critical electric field. E<sub>C</sub> depends on temperature and doping. A common figure of merit (FOM) for power devices is given by

$$FOM(Baliga) = V_B^2/R_{ON} = e\mu E_C^2.$$

(2)

The scaling of E<sub>c</sub> with bandgap is in the exponent range of 2-2.5. An alternative FOM often used is due to Huang and is a good predictor of power density in a variety of types of power converter, given by<sup>12</sup>

$$FOM(Huang) = E_C \mu^{0.5}.$$

(3)

This Baliga's figure of merit, 3400, is at least ten times larger than that of 4H-SiC and four times larger than that of GaN. These

Department of Materials Science and Engineering, University of Florida, Gainesville, Florida 32611

excellent high field properties make  $\beta\text{-}Ga_2O_3$  ideal for low loss, high-voltage switching and high-power applications, including high-breakdown voltage Schottky rectifiers and metal-oxide-semiconductor field-effect transistors.  $^{1,3,5,7,13-29}$  Schottky rectifiers have advantages for fast switching speeds and low forward voltage drops in comparison with p-n junction diodes, which can decrease the power loss and improve the efficiency of power supplies.  $^{30-41}$  In any case, the absence of p-type doping capability in  $Ga_2O_3$  makes implementation of junction difficult, since they require the use of heterojunctions with p-type oxides like NiO.  $^{42}$

Breakdown voltages in excess of 2 kV have been reported in β-Ga<sub>2</sub>O<sub>3</sub> Schottky rectifiers, but these are still below 30% of the ideal value. 14,17,19,20,35,36,43 The breakdown is still observed to occur at the periphery of the rectifying contact, 43 showing the need to reduce electric field crowding in order to fully realize the high voltage potential of β-Ga<sub>2</sub>O<sub>3</sub>. The dominant mechanism for the reverse leakage current in all the Ga<sub>2</sub>O<sub>3</sub> rectifiers to date is the emission of electrons through trap states located near the metalsemiconductor interface, governed by Poole-Frenkel emission.<sup>35</sup> In this regard, many edge termination methods have been adopted to reduce the maximum electric field near the contact edge, such as field plate, 13,14,17,24,28,43 trench MOS-type, 16,19,34,36 dielectric field plates,<sup>27</sup> bevel-field plate, <sup>18</sup> and implantation of guard ring structures to form high resistivity layers that reduce the field strength near the contact periphery. 21,22 <sup>2,30</sup> An understanding of the surface properties is also important in high field devices.

Another simple edge termination method, floating metal field ring (FMR),  $^{41}$  is commonly used in SiC and GaN Schottky diodes.  $^{50-52}$  These have an advantage in that they can be fabricated simultaneously with the Schottky contact. Previous work in  $\rm Ga_2O_3$  showed that vertical Schottky rectifiers with FMR edge termination were effective in enhancing breakdown voltage. As the distance between the Schottky contact and the electrically floating FMRs increased, the breakdown voltage was found to increase by 20%-45% in comparison with devices without the FMR. However, clearly there needs to be a more detailed investigation of the effects of FMR in terms of the number of rings, how they are biased, and their spacing and width.

In this paper, we report simulations of all these effects and compare the data with experimental values of breakdown in unterminated and FMR-terminated vertical rectifiers.

#### II. EXPERIMENT

#### A. Simulation

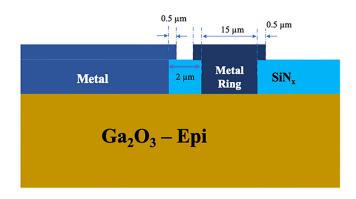

The device simulation has been performed using the FLOODS TCAD simulator, a self-consistent partial differential equation solver.  $^{44,46}$  The model used for the simulations involves solving for the electric field, and the device is simulated until the critical field strength (Ec) of the material is reached.  $^{44}$  The device structure used in this simulation consists of an  $n^+$  bulk  $\beta\text{-Ga}_2\text{O}_3$  on which an epitaxial layer of moderately doped n-type  $\beta\text{-Ga}_2\text{O}_3$  is grown. The bulk layer has a constant doping concentration of  $4.8\times10^{18}$  cm $^{-3}$  while the epilayer doping concentration is treated as a study parameter. The breakdown of the device is tested for three doping concentrations, i.e.,  $5\times10^{15}$ ,  $1\times10^{16}$ , and  $4\times10^{16}$  cm $^{-3}$ . The device has a dielectric layer of  $SiN_x$ , which is deposited to help in the

spreading of the electric field. A window is etched into the dielectric where is the metal ring is deposited to create a floating metal ring contact with the  $\rm Ga_2O_3$  epitaxial layer. In order to help with computation speeds, only half the device is simulated, and the bulk layer is thinned to  $10\,\mu{\rm m}$  as the breakdown characteristics are not dependent on the bulk layer thickness.

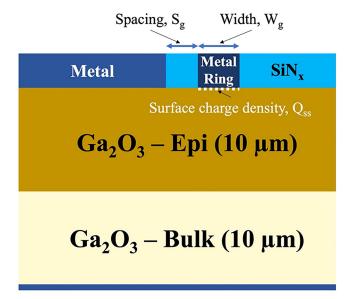

These simulations aim to help device engineers achieve the highest breakdown voltage while designing the  $\beta\text{-}Ga_2O_3$  Schottky diodes with metal rings. A simple cross section of the device can be seen in Fig. 1, and the important structural parameters like the spacing between the Schottky contact and metal ring  $(S_g)$  and width of the metal ring  $(W_g)$  have been highlighted. In this study, the breakdown characteristics are analyzed as a function of these structural parameters, the number of metal rings, and bias applied to these rings.

The device simulation is performed using reflective boundary conditions on left and right vertical surfaces, while Schottky and Ohmic boundary conditions have been set for the top and bottom contact, respectively. The metal ring contact has two boundary conditions based on the simulation, i.e., floating (fixed charge) and Schottky (for when the ring is biased with a negative potential) boundary conditions.

The floating contact has been simulated by defining a fixed charge at the metal ring and  $\rm Ga_2O_3$  interface. The surface charge density  $\rm Q_{ss}$  can be defined as  $^{44-46}$

$$Q_{ss} = -qD_s(E_g - q\phi_0 - q\phi_{Bn}), \tag{4}$$

where  $D_s$  is the acceptor surface states density per electron volt (states/cm<sup>2</sup> eV),  $E_g$  is the energy bandgap,  $\phi_0$  is the charge

**FIG. 1.** Schematic of the FMR structure employed for simulations. The surface charge density was varied to obtain floating contact conditions for the different drift layer doping concentrations.

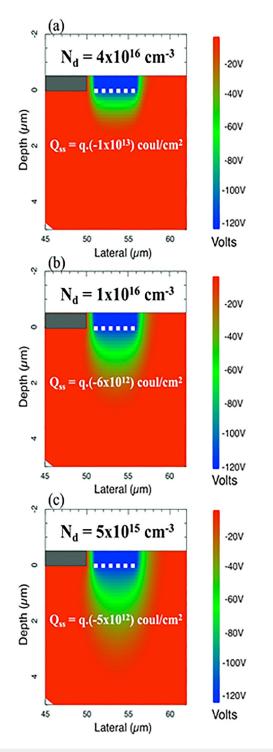

**FIG. 2.** Electrostatic potential distribution as a function of doping concentration and surface state density in the semiconductor at 0 V bias ( $S_g = 1.0 \, \mu m$ ,  $W_g = 5.0 \, \mu m$ ). The surface charge density is fit in order to achieve the same potential ( $-120 \, \text{V}$ ) developed at the metal ring/GaO interface.

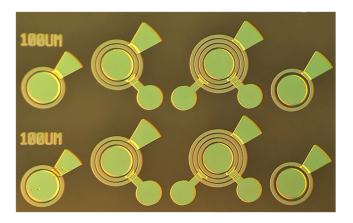

FIG. 3. Optical image of fabricated rectifier showing three field rings.

neutrality level, and  $\varphi_{Bn}$  is the barrier height of the metal-semiconductor barrier. The term in the parentheses is the difference between the surface Fermi level and the charge neutrality level.

To model the surface charge density for different doping concentrations, the change in the Fermi level and  $D_s$  has to be evaluated as a function of  $N_d$ . The gallium oxide surface has been the focus of many recent studies;  $^{45-47}$  however, the results are still inconclusive and depend largely on growth techniques. To maintain qualitative results, we assume a  $Q_{ss}$  of  $q\cdot (-1\times 10^{13})$  Coul/cm² for a device with  $N_d=4\times 10^{16}$  cm $^{-3}$ . The device is then simulated at 0 bias and the potential distribution as seen in Fig. 3(a) is obtained. In the device with lower doping concentration,  $Q_{ss}$  is fit by simulating the same potential (-120~V) developed under the metal ring, which can be seen in Figs. 2(a)–2(c) and summarized in Table I.

### **B.** Device fabrication

The starting material for diode fabrication was a  $10\,\mu m$  Si-doped  $(3.5\times 10^{16}\,cm^{-3}$  determined by capacitance-voltage measurements) epitaxial layer grown by halide vapor epitaxy on a  $650\,\mu m$  thick, (001) oriented, Sn-doped  $(n=3.6\times 10^{18}\,cm^{-3})$   $\beta\text{-Ga}_2\mathrm{O}_3$  wafer grown by the edge-defined film-fed growth method (Novel Crystal Technology). A 100 nm thick (20 nm/80 nm Ti/Au) back side ohmic contact was formed using an electron beam (e-beam) evaporator followed by 30 s rapid thermal annealing using an SSI SOLARIS 150 rapid thermal annealer in an  $N_2$  ambient at 550 °C.

**TABLE I.** Surface charge density corresponding to the drift layer doping concentration.

| Doping (cm <sup>-3</sup> )                                                                           | Surface charge density (cm <sup>-2</sup> )                                          |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| $\begin{aligned} N_d &= 5 \times 10^{15} \\ N_d &= 10^{16} \\ N_d &= 4 \times 10^{16} \end{aligned}$ | $ \begin{array}{r} -5 \times 10^{12} \\ -6 \times 10^{12} \\ -10^{13} \end{array} $ |

TABLE II. Breakdown voltage of device with and without T-gate/field plate structure.

| Doping (cm <sup>-3</sup> )                                        | Unterminated (V) | $S_g = 2$ and $W_g$<br>= 15 without<br>field plate<br>(V) | Optimized by<br>T-gates field plate<br>overlap of 0.5 μm<br>(V) |

|-------------------------------------------------------------------|------------------|-----------------------------------------------------------|-----------------------------------------------------------------|

| $N_d = 5 \times 10^{15}$ $N_d = 10^{16}$ $N_d = 4 \times 10^{16}$ | 610              | 770                                                       | 870                                                             |

|                                                                   | 475              | 590                                                       | 700                                                             |

|                                                                   | 290              | 355                                                       | 405                                                             |

Standard solvent cleaning and 20 min of O<sub>3</sub> cleaning were performed to remove hydrocarbon and other contaminants prior to Schottky metal deposition. The first layer of metal (100 nm/ 50 nm Ni/Au for Schottky contact and field rings) was deposited using an e-beam evaporator followed by standard acetone liftoff. For interlayer dielectrics, 40 nm Al<sub>2</sub>O<sub>3</sub> and 160 nm SiN<sub>x</sub> were deposited using a Cambridge-Nano-Fiji atomic layer deposition and Plasma-Therm plasma enhanced chemical vapor deposition tools. Dielectric openings for Schottky contact and selective regions on the field ring were formed using 1:10 buffered oxide etchant. A second layer of metal deposition (250 nm/100 nm Ni/Au) was performed using the e-beam evaporator on the Schottky contact and to form connections between individual field rings with external contact pads. Figure 3 shows a photograph of fabricated rectifiers with center Schottky diodes, field rings with a fixed ring width (wg) of  $10 \,\mu\text{m}$ , and their respective contact pads. Note that custom photomasks were designed individually for metal deposition and dielectric etching process. Electrical measurements were made using Agilent 4156 parameter analyzer and Tektronix 370A curve tracer. An optical microscope image of a rectifier with three field rings is shown in Fig. 3.

The Schottky barrier height  $\Phi$  was obtained from the slope of the linear region of the gate forward current-voltage (I–V) characteristics plotted on a log scale, through the relation<sup>49</sup>

$$\Phi = (k.T/e)x \ln (A^*xT^2xA)/I_{intercept},$$

(5)

where k is Boltzmann's constant, e is the electronic charge, A is the gate contact area equal to the product of gate length,  $A^*$  is Richardson's constant, and  $I_{intercept}$  is the intercept of the linear region with the voltage axis. The ideality factor is also obtained from the slope of the I–V characteristic.

# III. RESULTS AND DISCUSSION

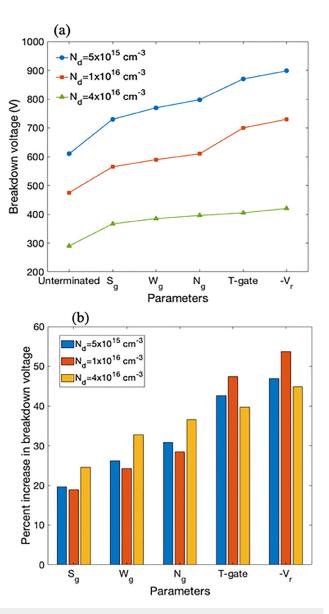

The breakdown of the device in TCAD is sensitive to the grid spacing, which typically results in qualitative results. Hence, to maintain homogeneity, the mesh for the device has been kept constant, especially near the areas of interest. The breakdown voltages of the unterminated diodes corresponding to the doping concentration are given in Table II. To analyze the effect of dimensionality of the floating metal ring structure, a set of simulations are performed, and the breakdown voltage is determined for each test case. The spacing between the Schottky contact and the metal ring is varied

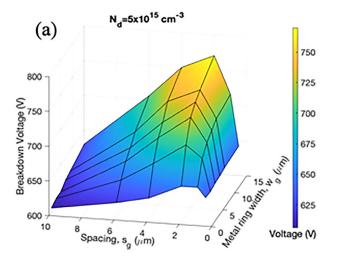

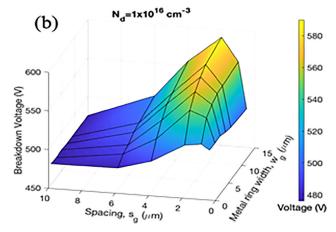

**FIG. 4.** Breakdown voltage as a function of field ring spacing  $S_g$  and width  $W_g$  for a single ring and drift layer doping of (a)  $5 \times 10^{15}$  cm $^{-3}$ , (b)  $10^{16}$  cm $^{-3}$ , and (c)  $4 \times 10^{16}$  cm $^{-3}$ .

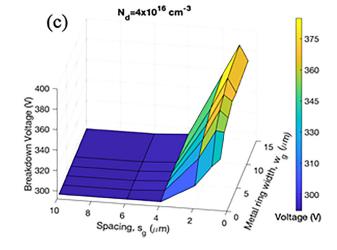

**FIG. 5.** Breakdown voltage as a function of field ring spacing S $_g$  and number of rings for a fixed ring width of  $2\,\mu\mathrm{m}$  and drift layer doping of (a)  $5\times10^{15}\,\mathrm{cm}^{-3}$ , (b)  $10^{16}\,\mathrm{cm}^{-3}$ , and (c)  $4\times10^{16}\,\mathrm{cm}^{-3}$ .

from 0 to  $10\,\mu\text{m}$ , while the width of the metal ring is varied from 1 to  $15\,\mu\text{m}$ .

Figures 4(a)–4(c) show a 3D surface plot color-coded to demonstrate the optimized values. For the samples with  $N_d = 5 \times 10^{15}$  and  $1 \times 10^{16}$  cm<sup>-3</sup>, the ideal value for the spacing ( $S_g$ ) is found to be  $2 \, \mu m$ , while for samples with  $N_d = 4 \times 10^{16}$  cm<sup>-3</sup>, the ideal value for the spacing is found to be  $1 \, \mu m$ . The key result here is that the

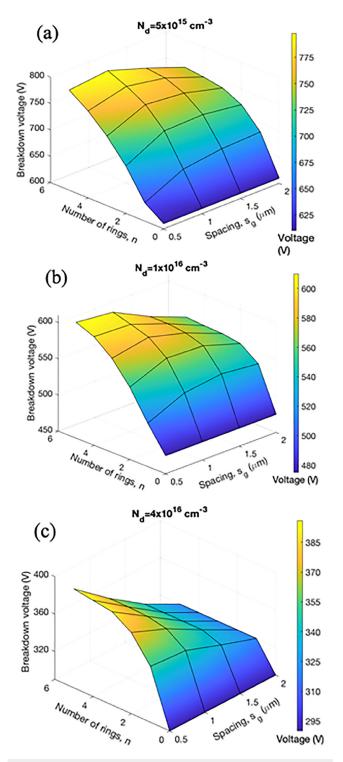

**FIG. 6.** (a) Breakdown voltage as a function of field ring bias voltage for a single ring width of  $2\,\mu m$  and drift layer doping of  $5\times 10^{15}$ ,  $10^{16}$ , or  $4\times 10^{16}$  cm<sup>-3</sup> and (b) peak electric field strength in the  $Ga_2O_3$  drift region as a function of the reverse bias on the rectifier and the stepped bias on the ring.

**FIG. 7.** Schematic of the FMR structure with T-gate/field plate extensions on the top Schottky and ring contacts.

higher doping samples ( $N_d = 4 \times 10^{16} \, cm^{-3}$ ) are very sensitive to  $S_g$ , and increasing  $S_g$  beyond  $3\,\mu m$  does not improve the breakdown voltage. The same effect can be expected for the lower doped samples, and this is attributed to  $S_g$  approaching the depletion width at breakdown. It can also be seen in the figure that as the width of the ring ( $W_G$ ) is increased, the breakdown voltage increases; however, the curves tend to saturate at high values of  $W_g$  ( $\sim 20\,\mu m$ ). As the width of the floating metal ring is increased, the total charge at the interface increases ( $Q_{ss}$  is the charge per unit area) linearly as a function of the width, which results in a higher potential being developed. The potential developed due to a charged surface conventionally follows a square root dependence on the total charge.

Studies on Schottky barrier diodes (SBDs) have demonstrated that adding multiple rings to the diode improves the breakdown characteristics of the diode.  $^{50-52}$  Gallium oxide SBDs have not yet been investigated in detail in terms of the metal rings around the Schottky metal; therefore, the effects of multiple rings on the breakdown voltage have been studied next. The device is simulated with a constant ring width of  $2\mu m$  while the number of rings and the spacing between them is varied. Figures 5(a)–5(c) illustrate the results of these simulations for three different values of  $N_d$ . As the number of rings  $(N_g)$  is increased from 1 to 5, the breakdown voltage also increases; however, a saturation effect is seen when  $N_g > 5$ , as the electric field distribution is not improved further. The simulations also reveal that as  $N_g$  is increased, the ideal spacing between the rings decreases, and for  $N_g = 5$ ,  $S_g$  is optimized

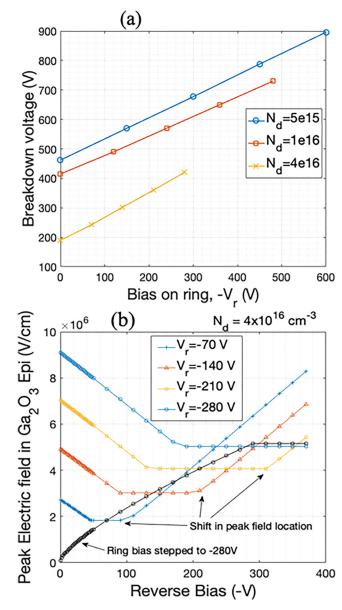

FIG. 8. (a) Simulated breakdown voltage and (b) percentage increase in breakdown voltage as a function of individual optimized parameters.

TABLE III. Summary of results.

|                            |                                       | Spacing (s <sub>g</sub> )                          | Width (w <sub>g</sub> )                                          | Number of rings (N <sub>g</sub> )                          | T-floating gate (field plate OL = 0.5) | Bias on ring (V)               |

|----------------------------|---------------------------------------|----------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|--------------------------------|

| Doping (cm <sup>-3</sup> ) | Unterminated<br>breakdown voltage (V) | $(\mu m) (w_g = 5)$<br>$V_{BD} (V)/\%$<br>increase | $(\mu m)$ (s <sub>g</sub> = ideal)<br>$V_{BD}$ (V)/%<br>increase | $(n = 5, w_g = 2, s_g = ideal)$<br>$V_{BD}$ (V)/% increase | V <sub>BD</sub> (V)/% increase         | V <sub>BD</sub> (V)/% increase |

| $5 \times 10^{15}$         | 610                                   | 730/19.7                                           | 770/26.2                                                         | 798/30.8                                                   | 870/42.6                               | 896/46.9                       |

| $10^{16}$                  | 475                                   | 565/18.9                                           | 590/24.2                                                         | 610/28.4                                                   | 700/47.4                               | 730/53.7                       |

| $4 \times 10^{16}$         | 290                                   | 367/26.6                                           | 385/32.8                                                         | 396/36.6                                                   | 405/39.7                               | 420/44.8                       |

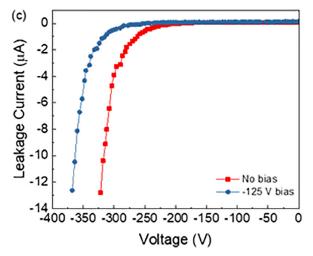

**FIG. 9.** (a) Forward I–V characteristics for a 100  $\mu$ m diameter diode with one field ring at 5  $\mu$ m field ring spacing (S<sub>g</sub>), (b) diode leakage current at -100 V as a function of ring reverse bias voltage, and (c) comparison of reverse I–V for the identical diode with and without ring bias at -125 V.

to  $1 \,\mu\mathrm{m}$  for  $N_{\rm d} = 5 \times 10^{15}$  and  $0.5 \,\mu\mathrm{m}$  for  $N_{\rm d} = 1 \times 10^{16}$  and  $4 \times 10^{16} \,\mathrm{cm}^{-3}$ .

In order to emulate the floating metal contacts, a negative bias can be applied on the rings, which can give device engineers better control over the breakdown. The relationship between the breakdown voltage ( $V_{bd}$ ) and bias on rings ( $V_r$ ) can be seen in Fig. 6(a) for the three doping concentrations. The reverse bias on the ring has been varied from 0 to the unterminated diodes breakdown voltage. However, as seen in Fig. 6(b), for a diode with  $N_d = 4 \times 10^{16} \ cm^{-3}$ , a larger reverse bias on the ring results in early breakdown due to a peak in the electric field under the metal ring. This can be overcome by ramping the bias on the ring, which would limit the electric fields under the contacts, as seen in the black data lines in Fig. 6(b).

Field plates have traditionally been very successful in improving breakdown characteristics of power semiconductor devices. As a simple extension to this study, a combination of floating metal rings and field plates on the  $\beta\text{-}\text{Ga}_2\text{O}_3$  SBDs is considered. The device is simulated with one floating metal ring while also employing a T-gate/field plate structure as seen in Fig. 7 with the dimensional parameters. This results in further improvement in  $V_{bd}$  as shown in Table II, as compared to the same structure without the field plate overlaps.

The results of this study are summarized in Table III, and applying a large reverse bias on the metal rings shows the best results; however, applying a bias on the rings may result in an early breakdown. In terms of floating contacts, a 40%–50% rise in the breakdown voltage is observed when a T-gate/field plate structure is also employed. Figures 8(a) and 8(b) help in visualizing the results where each parameter is optimized based on the results of the simulations.

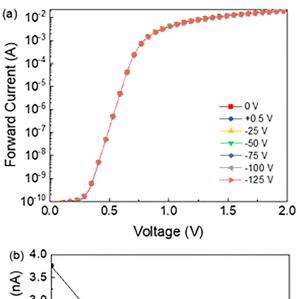

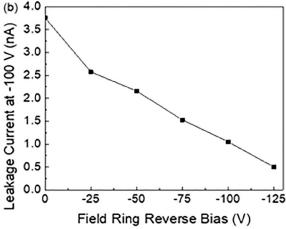

Figure 9(a) shows the forward I–V characteristics for a  $100\,\mu\mathrm{m}$  devices with one field ring and  $S_g = 5\,\mu\mathrm{m}$ . The overlapping forward I–V for various ring bias conditions (range from +0.5 to -125 V) suggest that applying bias on the field ring as edge termination does not have a significant impact on forward bias characteristics. Table IV shows that all of these curves share comparable Schottky barrier height (1.03 eV), ideality factor (1.03), and on resistance (4.5–4.9 m $\Omega$  cm $^2$ ). From reverse I–V measurements down to -100 V, a substantial reduction in leakage current has been observed upon biasing the first surrounding field ring with negative

**TABLE IV.** Summary of diode parameters for single  $100\,\mu\mathrm{m}$  diameter diode with one field ring at  $5\,\mu\mathrm{m}$  field ring spacing (S<sub>q</sub>) at different ring bias conditions.

| Ring bias |          | Schottky    | On               | On-off ratio         |

|-----------|----------|-------------|------------------|----------------------|

| voltage   | Ideality | barrier     | resistance       | (current at          |

| (V)       | factor   | height (eV) | $(m\Omega cm^2)$ | +2/-100 V)           |

| 0         | 1.03     | 1.03        | 4.5              | $5.51 \times 10^{6}$ |

| +0.5      | 1.03     | 1.03        | 4.5              | _                    |

| -25       | 1.03     | 1.03        | 4.6              | $7.91 \times 10^{6}$ |

| -50       | 1.03     | 1.03        | 4.7              | $9.28 \times 10^{6}$ |

| -75       | 1.03     | 1.03        | 4.8              | $1.29 \times 10^{7}$ |

| -100      | 1.03     | 1.03        | 4.8              | $1.86 \times 10^{7}$ |

| -125      | 1.03     | 1.03        | 4.9              | $3.86 \times 10^{7}$ |

potential. Figure 9(b) presents the reverse leakage current at -100 V at various ring bias voltages, suggesting an 87% decrease in diode leakage current upon biasing the first field ring ( $S_g = 5 \mu m$ ) up to −125 V. Table IV shows that upon biasing the first field ring to -125 V, a seven times increase in device on-off ratio has been observed without major impact to device turn-on characteristics, and therefore gives rise to a higher device breakdown voltage with consistent device performance. Figure 9(c) shows the breakdown voltage for the identical diode using 10 µA as leakage current compliance. A net 14% of breakdown voltage increase was observed. Note that no reverse bias measurement was made between the 0 and -125 V scan to prevent degradation of diode due to repeated measurement. Diodes with field rings of less than  $5 \mu m$  were not fabricated in this work due to processing limitations, and meanwhile, diodes with spacing  $S_g$  larger than  $5 \mu m$ , as well as individually biasing the second and third field ring only, show lower percentages of leakage current reduction, as suggested in previous simulations.

#### IV. SUMMARY AND CONCLUSIONS

Simulations have been performed to investigate the effect of floating and biased metal rings for edge termination on  $Ga_2O_3$  rectifiers. The effects of varying ring spacing, width, number of rings, addition of field plate in conjunction with the rings, and biasing of the rings were investigated. The breakdown voltage can be increased by up to a factor of 54% from the unterminated case. The choice of edge termination method is also dictated by the complexity of the additional processing steps needed, but a combination of field plates and field rings is relatively straightforward to implement. Experimental verification of the efficacy of the FMRs has been demonstrated using one, two, or three rings.

#### **ACKNOWLEDGMENTS**

The work at the UF was sponsored by Department of the Defense, Defense Threat Reduction Agency (Nos. HDTRA1-17-1-011 and HDTRA1-20-2-0002) monitored by J. Calkins. The content of the information does not necessarily reflect the position or the policy of the federal government, and no official endorsement should be inferred. It was also sponsored by NSF [No. DMR 1856662 (James Edgar)]. Research at NRL was supported by the Office of Naval Research (ONR).

# DATA AVAILABILITY

The data that support the findings of this study are available within the article.

#### **REFERENCES**

- <sup>1</sup>D. A. Oulianov, R. A. Crowell, D. J. Gosztola, I. A. Shkrob, O. J. Korovyanko, and R. C. Rey-de-Castro, J. Appl. Phys. **101**, 053102 (2007); M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. **31**, 034001 (2016).

- <sup>2</sup>H. von Wenckstern, Adv. Electron. Mater. 3, 1600350 (2017).

- <sup>3</sup>S. J. Pearton, J. Yang, P. H. Carey IV, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, Appl. Phys. Rev. 5, 011301 (2018).

- <sup>4</sup>Z. Galazka, Semicond. Sci. Technol. 33, 113001 (2018).

- <sup>5</sup>M. Higashiwaki and G. H. Jessen, Appl. Phys. Lett. 112, 060401 (2018).

- <sup>6</sup>J. L. Lyons, Semicond. Sci. Technol. 33, 05LT02 (2018).

- J. Pearton, F. Ren, M. Tadjer, and J. Kim, J. Appl. Phys. 124, 220901 (2018).

J. Zhang, J. Shi, D.-C. Qi, L. Chen, and K. H. L. Zhang, APL Mater. 8, 020906

- <sup>8</sup>J. Zhang, J. Shi, D.-C. Qi, L. Chen, and K. H. L. Zhang, APL Mater. **8**, 020906 (2020).

- <sup>9</sup>R. J. Kaplar, A. A. Allerman, A. M. Armstrong, M. H. Crawford, J. R. Dickerson, A. J. Fischer, A. G. Baca, and E. A. Douglas, ECS J. Solid State Sci. Technol. **6**, Q3061 (2017).

- 10 A. G. Baca, A. M. Armstrong, B. A. Klein, A. A. Allerman, E. A. Douglas, and R. J. Kaplar, J. Vac. Sci. Technol. A 38, 020803 (2020).

- 11 R. J. Kaplar, O. Slobodyan, J. D. Flicker, and M. A. Hollis, 236th ECS Meeting, Atlanta, GA, October 2019 (The Electrochemical Society, Pennington, NJ, 2019).

12 Alex Q. Huang, IEEE Electron Device Lett. 25, 298 (2004).

- <sup>13</sup>K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. 110, 103506 (2017).

- <sup>14</sup>J. Yang, F. Ren, M. Tadjer, S. J. Pearton, and A. Kuramata, ECS J. Solid State Sci. Technol. 7, Q92 (2018).

- <sup>15</sup>Z. Hu *et al.*, Appl. Phys. Lett. **113**, 122103 (2018).

- <sup>16</sup>W. Li et al., Appl. Phys. Lett. **113**, 202101 (2018).

- <sup>17</sup>Z. Hu, H. Zhou, Q. Feng, J. Zhang, C. Zhang, K. Dang, Y. Cai, Z. Feng, Y. Gao, X. Kang, and Y. Hao, IEEE Electron Device Lett. 39, 1564 (2018).

- <sup>18</sup>C. Joishi, S. Rafique, Z. Xia, L. Han, S. Krishnamoorthy, Y. Zhang, S. Lodha, H. Zhao, and S. Rajan, Appl. Phys. Express 11, 031101 (2018).

- <sup>19</sup>W. Li et al., 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 1–5 Dec. 2018 (IEEE, New York, 2018).

- <sup>20</sup>W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. G. Xing, 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 7–11 December 2019 (IEEE, New York, 2019), pp. 12.4.1–12.4.4.

- <sup>21</sup>C.-H. Lin et al., IEEE Electron Device Lett. **40**, 1487 (2019).

- <sup>22</sup>M. H. Wong, H. Murakami, Y. Kumagai, and M. Higashiwaki, IEEE Electron Device Lett. 41, 296 (2020).

- <sup>23</sup>K. Ghosh and U. Singisetti, J. Appl. Phys. 24, 085707 (2018).

- <sup>24</sup>J. Yang, F. Ren, M. Tadjer, S. J. Pearton, and A. Kuramata, AIP Adv. 8, 055026 (2018).

- <sup>25</sup>R. Sharma, E. E. Patrick, M. E. Law, F. Ren, and S. J. Pearton, ECS J. Solid State Sci. Technol. 8, Q234 (2019).

- <sup>26</sup>N. Allen, M. Xiao, X. Yan, K. Sasaki, M. J. Tadjer, J. Ma, R. Zhang, H. Wang, and Y. Zhang, IEEE Electron Device Lett. 40, 1399 (2019).

- <sup>27</sup>P. H. Carey IV, J. Yang, F. Ren, R. Sharma, M. Law, and S. J. Pearton, ECS J. Solid State Sci. Technol. 8, Q3221 (2019).

- <sup>28</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, IEEE Electron Device Lett. 37, 212 (2016).

- 29 K. Zeng, A. Vaidya, and U. Singisetti, Appl. Phys. Express 12, 081003 (2019).

- 30 Y. Gao et al., Nanoscale Res. Lett. 14, 8 (2019).

31 M. J. Tadjer et al., Proc. SPIE 10532, 1053212 (2018).

- <sup>32</sup>Z. Islam, A. Haque, N. R. Glavin, M. Xian, F. Ren, A. Y Polyakov, A. I. Kochkova, M. Tadjer, and S. J. Pearton, ECS J. Solid State Sci. Technol. 9, 055008 (2020).

- Xia, H. Chandrasekar, W. Moore, C. Wang, A. J. Lee, J. McGlone, N. K. Kalaricka, A. Arehart, and S. Ringel, Appl. Phys. Lett. 115, 252104 (2019).

H. Okumura and T. Tanaka, Jpn. J. Appl. Phys. 58, 120902 (2019).

- 35W. Li, D. Saraswat, Y. Long, K. Nomoto, D. Jena, and H. G. Xing, Appl. Phys. Lett. 116, 192101 (2020).

- 36W. Li, K. Nomoto, Z. Hu, D. Jena, and H. G. Xing, IEEE Electron Device Lett. 41, 107 (2020).

- 37 Z. Islam, M. Xian, A. Haque, F. Ren, M. Tadjer, N. Glavin, and S. J. Pearton,

- IEEE Trans. Electron Devices 67, 3056 (2020).

38 M. Xian, C. Fares, F. Ren, Z. Islam, A. Haque, M. Tadjer, and S. J. Pearton, ECS J. Solid State Sci. Technol. 9, 035007 (2020).

- 39 L. Zhou, X. Lu, L. Chen, X. Ouyang, B. Liu, J. Xu, and H. Tang, ECS J. Solid

- State Sci. Technol. 8, Q3054 (2019).

<sup>40</sup>A. Y. Polyakov, I.-H. Lee, N. B. Smirnov, I. V. Shchemerov, A. Vasilev,

- A. V. Chernykh, and S. J. Pearton, J. Phys. D Appl. Phys. 53, 304001 (2020).

- <sup>41</sup>Z. Hu et al., ECS J. Solid State Sci. Technol. **9**, 025001 (2020).

- <sup>48</sup>J. E. N. Swallow, J. B. Varley, L. A. H. Jones, J. T. Gibbon, L. F. J. Piper, V. R. Dhanak, and T. D. Veal, APL Mater. 7, 022528 (2019).

49

S. K. Cheung and N. W. Cheung, Appl. Phys. Lett. 49, 85

- (1986).

- 50 S. C. Chang, S. J. Wang, K. M. Uang, and B. W. Liou, Solid State Electron. 49, 437 (2005).

51 J. Wang *et al.*, Mater. Sci. Semicond. Proc. **97**, 101 (2019).

- 52C. Zhou, X. Luo, X. Deng et al., 2006 8th International Conference on Solid-State and Integrated Circuit Technology Proceedings, Shanghai, China, 23-26 October 2006 (IEEE, New York, 2006), pp. 944-946.

<sup>42</sup>H. H. Gong, X. H. Chen, Y. Xu, F.-F. Ren, S. L. Gu, and J. D. Ye, Appl. Phys. Lett. 117, 022104 (2020).

<sup>43</sup> J. Yang, C. Fares, R. Elhassani, M. Xian, F. Ren, S. J. Pearton, M. Tadjer, and A. Kuramata, ECS J. Solid State Sci. Technol. 8, Q3159 (2019).

M. E. Law and S. M. Cea, Comput. Mater. Sci. 12, 289 (1998).

<sup>45</sup> J. Kim, F. Ren, and S. J. Pearton, Nanoscale Horiz. 4, 1251 (2019).

<sup>&</sup>lt;sup>46</sup>S. M. Sze and K. N. Kwok, *Physics of Semiconductor Devices* (Wiley,

New York, 2006). 47R. Lingaparthia, Q. T. Thieu, K. Koshi, D. Wakimoto, K. Sasaki, and A. Kuramata, Appl. Phys. Lett. 116, 092101 (2020).